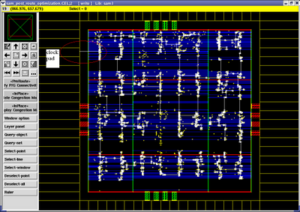

Physical design (electronics)

|

Read other articles:

Este artículo o sección necesita referencias que aparezcan en una publicación acreditada.Este aviso fue puesto el 10 de septiembre de 2017. Philip José Farmer Información personalNacimiento 26 de enero de 1918 o 1918 Terre Haute (Indiana, Estados Unidos) Fallecimiento 25 de febrero de 2009 Peoria (Illinois, Estados Unidos) Nacionalidad EstadounidenseLengua materna Inglés EducaciónEducado en Universidad BradleyPeoria High School Información profesionalOcupación Novelista, escritor de ...

Popular American law dictionary Black's Law Dictionary Image of the 7th editionEditorBryan A. Garner(1999–present)CountryUnited StatesLanguageEnglishPublisherWest (Thomson Reuters)Publication date1891 (1st)1910 (2nd)1933 (3rd)1951 (4th)1968 (4thR)1979 (5th)1990 (6th)1999 (7th)2004 (8th)2009 (9th)2014 (10th)2019 (11th)ISBN978-1-5392-2975-9WebsiteBlack's Law Dictionary Black's Law Dictionary is the most frequently used legal dictionary in the United States.[1] Henry Campbell Black...

Metro station in Delhi, India This article is about the metro station in Delhi, India. For metro station in Hyderabad, see Stadium metro Station. Jawaharlal Nehru Stadium Delhi Metro stationGeneral informationLocationPragati Vihar, New Delhi, 110003Coordinates28°35′25.372″N 77°13′58.976″E / 28.59038111°N 77.23304889°E / 28.59038111; 77.23304889Owned byDelhi MetroLine(s)Violet LinePlatformsIsland platformPlatform-1 → Raja Nahar SinghPlatform-2 → Kashmere...

Глорія Гвідаітал. Gloria Guida Народилася 19 листопада 1955(1955-11-19) (68 років)Мерано, ІталіяГромадянство ІталіяДіяльність акторка, модель, співачкаРоки діяльності з 1974 рокуЧоловік Джоні Дореллі (1981)Діти донькаIMDb ID 0346708 Глорія Гвіда у Вікісховищі Висловлювання у Вік�...

Himno Nacional Paraguayo Paraguayos, ¡República o Muerte! العنوان بالعربية نشيد باراغواي الوطني العنوان بالإنجليزية Paraguayan National Anthem البلد باراغواي اللغة الإسبانية استمع للنشيد تعديل مصدري - تعديل نشيد باراغواي الوطني (بالإسبانية:Himno Nacional Paraguayo)، هو النشيد الوطني لدولة الباراغواي.[1...

Si ce bandeau n'est plus pertinent, retirez-le. Cliquez ici pour en savoir plus. Cet article ne s'appuie pas, ou pas assez, sur des sources secondaires ou tertiaires (août 2023). Pour améliorer la vérifiabilité de l'article ainsi que son intérêt encyclopédique, il est nécessaire, quand des sources primaires sont citées, de les associer à des analyses faites par des sources secondaires. Internet Speculative Fiction DatabaseHistoireFondation 1995CadreType Base de données en ligne, ba...

مغامرون حول العالممعلومات عامةالصنف الفني كوميديتاريخ الصدور 1978مدة العرض 100 دقيقةاللغة الأصلية العربيةالبلد مصرالطاقمالمخرج محمود فريدالكاتب فيصل ندابهجت قمرالبطولة ناهد شريفعادل إماملبلبةسمير غانمالتصوير رمزي إبراهيمالموسيقى ميشيل يوسفالتركيب فكري رستمصناعة س�...

Public school in Newport, Perry County, Pennsylvania, United StatesNewport High SchoolAddress500 Caroline StNewport, Perry County, Pennsylvania 17074-0009United StatesInformationTypePublicSchool districtNewport School DistrictPrincipalMr. Scott McGradyFaculty26 teachers[1]Grades9-12Number of students311 pupils (2016)[2]Education systemNewport School DistrictLanguageEnglishCommunities servedNewport, PennsylvaniaFeeder schoolsNewport Middle School (same building)Websitehttp://ww...

1765 British statute which taxed its American colonies' use of printed materials United Kingdom legislationStamp Act 1765Act of ParliamentParliament of Great BritainLong titleAn Act for granting and applying certain stamp duties, and other duties, in the British colonies and plantations in America, towards further defraying the expenses of defending, protecting, and securing the same; and for amending such parts of the several Acts of Parliament relating to the trade and revenues of the said ...

Speech by US president Dwight D. Eisenhower This article relies largely or entirely on a single source. Relevant discussion may be found on the talk page. Please help improve this article by introducing citations to additional sources.Find sources: 1956 State of the Union Address – news · newspapers · books · scholar · JSTOR (September 2021) The 1956 State of the Union Address was given by Dwight D. Eisenhower, the 34th president of the United States, ...

1985 Indian filmPournami AlaigalPosterDirected byM. BhaskarWritten byM. BhaskarProduced byM. BhaskarStarringSivakumarAmbikaRevathiCinematographyViswam NatarajEdited byM. VellaichamiMusic byShankar–GaneshProductioncompanyOscar MoviesRelease date 12 January 1985 (1985-01-12) CountryIndiaLanguageTamil Pournami Alaigal (transl. Full moon waves) is a 1985 Indian Tamil-language legal thriller film produced, written and directed by M. Bhaskar. The film stars Sivakumar, Ambika ...

Laguna Brava FormationStratigraphic range: Late Eocene (Tinguirirican)TypeGeological formationOverliesQuebrada Santo Domingo FormationLithologyPrimarySandstone, red beds, tuffLocationCoordinates28°30′S 68°48′W / 28.5°S 68.8°W / -28.5; -68.8Approximate paleocoordinates30°36′S 60°36′W / 30.6°S 60.6°W / -30.6; -60.6RegionMendoza Province, Argentine NorthwestCountryArgentinaExtentPrecordilleraType sectionNamed forLaguna BravaLaguna B...

1920 film by Harley Knoles Guilty of LoveFilm still with DaltonDirected byHarley KnolesScreenplay byRosina HenleyBased onThis Woman — This Manby Avery Hopwood[1]Produced byAdolph ZukorStarringDorothy DaltonJulia HurleyHenry CarvillCinematographyPhilip HatkinProductioncompanyFamous Players–Lasky CorporationDistributed byParamount PicturesRelease date August 22, 1920 (1920-08-22) Running time50 minutesCountryUnited StatesLanguageSilent (English intertitles) Guilty of ...

Uruguayan footballer (1902-1968) Santos Iriarte Iriarte with Uruguay in 1930.Personal informationFull name Victoriano Santos IriarteDate of birth (1902-11-02)November 2, 1902Place of birth Canelones, UruguayDate of death November 10, 1968(1968-11-10) (aged 66)Place of death Montevideo, UruguayPosition(s) ForwardSenior career*Years Team Apps (Gls)1923–1932 Racing Montevideo 423 (34)1932–1934 Peñarol 156 (30)Total 579 (64)International career1930–1931 Uruguay 5 (2) Medal record Men'...

Use of the nude human form to further political or social change 1903 protest of Canadian immigration policy change, by Spiritual Christian Freedomites in Saskatchewan. Nude people protesting San Francisco's nudity ban Nudity is sometimes used as a tactic during a protest to attract media and public attention to a cause, and sometimes promotion of public nudity is itself the objective of a nude protest.[1] The practice was first documented in the 1650s with Quakers naked as a sign pra...

Конкурс молодых музыкантов «Евровидение-1998» Даты Финал 4 июня 1998 Проведение Место проведения Австрия, Вена, «Венский Концертхаус» Ведущие Юлиан Рахлин Дирижёр Деннис Рассел Дэвис Основной вещатель ORF Интервал-акт Выступление Юлиана Рахлина Участники Всего участник�...

1960 film The Deadly CompanionsTheatrical release posterDirected bySam PeckinpahWritten byA. S. FleischmanBased onThe Deadly Companionsby A. S. FleischmanProduced byCharles B. FitzsimonsStarringMaureen O'HaraBrian KeithSteve CochranChill WillsStrother MartinWill WrightCinematographyWilliam H. ClothierEdited byStanley RabjohnMusic byMarlin SkilesProductioncompanyCarousel ProductionsDistributed byPathé-America Distributing Company (US)Warner Bros. Pictures (International)Release date June ...

Tokyo 2020 dan Olimpiade 2021 dialihkan ke halaman ini. Untuk Paralimpiade Musim Panas, lihat Paralimpiade Musim Panas 2020. Untuk partisipasi Indonesia dalam kompetisi ini, lihat Indonesia pada Olimpiade Musim Panas 2020. Olimpiade XXXIITuan rumahTokyo, JepangMoto United by Emotion (Disatukan oleh Emosi) Jumlah negara205Jumlah atlet11,090[1]Jumlah disiplin339 di 33 olahraga (50 disiplin)Pembukaan23 Juli 2021Penutupan8 Agustus 2021Dibuka olehKaisar NaruhitoKaldronNaomi OsakaStadionSta...

2001 greatest hits album by Ol' Dirty BastardThe Dirty Story: The Best of Ol' Dirty BastardGreatest hits album by Ol' Dirty BastardReleasedAugust 28, 2001GenreHip hopLabelElektra[1]ProducerThe Neptunes, RZA, Ol' Dirty Bastard, True Master, Dat Nigga Reb, Irv Gotti, Flavahood Professional ratingsReview scoresSourceRatingAllMusic[2]The New Rolling Stone Album Guide[3] The Dirty Story: The Best of Ol' Dirty Bastard is a greatest hits album by Ol' Dirty Bastard. ...

American rock group The Bloodhound Gang redirects here. For the segment on the TV show 3-2-1 Contact, see The Bloodhound Gang (TV series). Bloodhound GangThe Bloodhound Gang performing in 1999Background informationAlso known asBang Chamber 8 (1988–1992)OriginPennsylvania, U.S.Genres Alternative rock comedy rock rap rock Years active1992–present[1]Labels Columbia SME Republic Geffen Interscope Universal Past membersSee members listWebsitebloodhoundgang.com The Bloodhound Gang is an...