Operand

|

Read other articles:

Ruscus hypoglossum met vruchten op de cladodiën. stengel van Homalocladium platycladum Cladodiën, die er uit zien als bladeren bij Phyllocladus alpinus Cladodiën (enkelvoud: cladodium, synoniemen: cladofyl, fyllocladium[1]) zijn stengels die een sterk bladachtig uiterlijk hebben. De echte bladeren zelf zijn dan vaak zeer sterk gereduceerd in vorm. De cladodiën hebben vele functies van de bladeren overgenomen en zijn dus fotosynthetisch actief. Cladodiën zijn echter stengels, daar...

この項目では、行政官庁について説明しています。その庁舎については「新潟県庁舎」をご覧ください。 新潟県の行政機関新潟県庁 新潟県庁役職知事 花角英世副知事 溝口洋高井盛雄益田浩組織知事部局 知事政策局総務管理部県民生活・環境部防災局福祉保健部産業労働観光部農林水産部農地部交通政策局土木部出納局行政委員会 教育委員会 (教育庁)公安委員会 (...

Aeropuerto Internacional de Babushara Междунароный аэропорт Бабушара IATA: SUI OACI: UGSS FAA: LocalizaciónUbicación Distrito de Gulripsh, GeorgiaElevación 16Sirve a Sujum AbjasiaDetalles del aeropuertoTipo Civil/MilitarOperador Empresa estatal Abkhaz AirlinesPistas DirecciónLargoSuperficie12/303,661 х 45Concreto reforzadoMapa SUI / UGSS[editar datos en Wikidata] El Aeropuerto Internacional de Babushara (ruso: Междунароный аэропорт

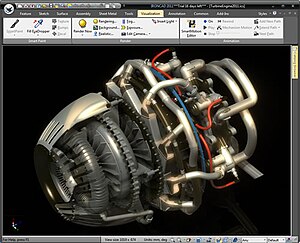

This article needs additional citations for verification. Please help improve this article by adding citations to reliable sources. Unsourced material may be challenged and removed.Find sources: Assembly modelling – news · newspapers · books · scholar · JSTOR (February 2022) (Learn how and when to remove this template message) An assembly. Assembly modeling is a technology and method used by computer-aided design and product visualization computer soft...

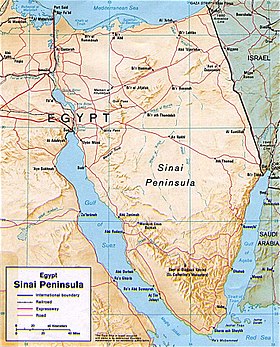

Peta semenanjung Sinai dengan batas-batas negara. Semenanjung Sinai (Arab: شبه جزيرة سيناء, singkatnya: سيناء, sīnā' ; Ibrani: סיני, sinei) adalah sebuah semenanjung berbentuk segitiga yang terletak di Asia Barat namun menjadi bagian dari Mesir di Afrika. Daratan seluas 60.000 km2 ini dibatasi oleh Laut Tengah di utara, Laut Merah di selatan, Terusan Suez di barat, dan perbatasan dengan Israel dan Jalur Gaza Palestina di timur laut. Daerah ini menjadi peng...

بطولة العالم لألعاب القوى داخل الصالات 2010 البلد قطر المدينة المضيفة الدوحة الدول المشاركة 146 الرياضيون المشاركون 585 التاريخ 2010 المكان قبة أكاديمية التفوق الرياضي الرياضة ألعاب القوى الأحداث بطولة العالم لألعاب القوى داخل الصالات 2010 – سيدات 4 × 400 متر تناوب ...

Singaporean cultural phrase Five Cs of Singapore — namely, cash, car, credit card, condominium and country club membership — is a phrase used in Singapore to refer to materialism.[1] It was coined as a popular observational joke during the 1990s about the aspirations of some Singaporeans to obtain material possessions in an effort to impress others.[2] In comparison, the CMPHH — namely, coin, MRT, public parks, HDB and hawker — is a phrase used in Singapore to refer to...

SEPTA Regional Rail line from Philadelphia to Doylestown Lansdale/Doylestown LineJenkintown–Wyncote station, a major stop on the Lansdale/Doylestown line in Jenkintown, PennsylvaniaOverviewStatusOperatingLocalePhiladelphiaMontgomery CountyBucks CountyTermini30th Street StationDoylestownStations28Websitesepta.orgServiceTypeCommuter railSystemSEPTA Regional RailRoute numberR5 Doylestown and R5 Lansdale (1984–2010)Operator(s)SEPTADepot(s)SEPTA Yards and maintenance facilitiesRolling stoc...

Argentine TV series or program SimonaGenreTelenovela Comedy MusicCreated byAdrián SuarWritten byClaudio LacelliLily Ann MartinDirected byRodolfo AntúnezSebastián PivottoStarringÁngela TorresGastón SoffrittiJuan DarthésAna María OrozcoRomina GaetaniAgustín CasanovaRenato QuattordioTheme music composerFlorencia Bertotti Willie LorenzoOpening themeSimona Va by Ángela TorresCountry of originArgentinaOriginal languageSpanishNo. of episodes154ProductionProducerAdrián SuarProduction l...

Bureau of Agricultural ResearchKawanihan ng Pananaliksik sa AgrikulturaAgency overviewFormedJanuary 30, 1987[1]HeadquartersRDMIC Building, Visayas Avenue corner Elliptical Road, Vasra, Quezon City 1104, Philippines14°39′17″N 121°02′52″E / 14.65468°N 121.04771°E / 14.65468; 121.04771Annual budget₱1.17 billion Php (2018)[2]Agency executiveJoell H. Lales, OIC-DirectorParent agencyDepartment of AgricultureWebsitewww.bar.gov.ph The Philippines'...

1985 film by Herb Freed TomboyTheatrical release posterDirected byHerb FreedScreenplay byHerb FreedBen ZeligStory byBen ZeligProduced byMichael D. CastleMarilyn Jacobs TenserStarring Betsy Russell Jerry DiNome Kristi Somers Richard Erdman Philip Sterling CinematographyDaniel YarussiEdited byRichard E. WestoverMusic byMichael LloydDistributed byCrown International PicturesBCI EclipseRelease date January 25, 1985 (1985-01-25) Running time91 minutesCountryUnited StatesLanguageEngl...

388th Rifle DivisionActive1941–1946Country Soviet UnionBranchRed ArmyTypeDivisionRoleInfantryEngagementsSiege of SevastopolSoviet invasion of ManchuriaBattle honoursHarbin (2nd Formation)CommandersNotablecommandersAleksandr Dmitrievich OvseenkoKombrig Semyon MonakhovNikolai Aleksandrovich ShvarevNikolai Fedorovich MulinMilitary unit The 388th Rifle Division was raised in 1941 as an infantry division of the Red Army, and served twice during World War II in that role. The division f...

Notable war correspondents This is a dynamic list and may never be able to satisfy particular standards for completeness. You can help by adding missing items with reliable sources. 19th century Archibald Forbes Benjamin C. Truman Bennet Burleigh (1840–1914), Sudan (Omdurman), Boer War, Russo-Japanese War, Italo-Turkish war Charles Frederick Williams, British journalist. Ferdinando Petruccelli della Gattina, Expedition of the thousand, Second and Third Italian War of Independence, Paris Com...

Play by William Shakespeare This article is about Shakespeare's play. For other uses, see Cymbeline (disambiguation). Imogen in her bedchamber in Act II, scene ii, when Iachimo witnesses the mole under her breast. Painting by Wilhelm Ferdinand Souchon, 1872 Cymbeline /ˈsɪmbɪliːn/, also known as The Tragedie of Cymbeline or Cymbeline, King of Britain, is a play by William Shakespeare set in Ancient Britain (c. 10–14 AD)[a] and based on legends that formed part of the Matter...

Japanese comedy duo WagyuNative name和牛 (Wagyū)Years active2006–presentEmployerYoshimoto KogyoGenresManzaiConteMembers Shinji Mizuta (Boke) Kenshiro Kawanishi (Tsukkomi) Same year/generation as:KamaitachiTenjiku NezumiFujisaki MarketAkinaEinsteinBike Kawasaki Bike Wagyu (和牛, Wagyū) is a Japanese comedy duo (kombi) consisting of Shinji Mizuta (水田信二) and Kenshirō Kawanishi (川西賢志郎). They are employed by Yoshimoto Kogyo, and are mainly active in Tokyo. They...

Sporting event delegationDemocratic Republic of the Congo at the2000 Summer OlympicsFlag of the Democratic Republic of the CongoIOC codeCODNOCComité Olympique Congolaisin SydneyCompetitors2 in 1 sportFlag bearer Willy Kalombo MwenzeMedals Gold 0 Silver 0 Bronze 0 Total 0 Summer Olympics appearances (overview)19681972–198019841988199219962000200420082012201620202024 The Democratic Republic of the Congo competed at the 2000 Summer Olympics in Sydney, Australia. Athletics Main article: A...

Ethnic groups from Madagascar This article is about the ethnic groups of Madagascar. For their language, see Malagasy language. For the residents or citizens of Madagascar, see Demographics of Madagascar. This article needs additional citations for verification. Please help improve this article by adding citations to reliable sources. Unsourced material may be challenged and removed.Find sources: Malagasy peoples – news · newspapers · books · scholar ·...

British writer Brooke MagnantiBrooke Magnanti on 7 June 2010BornBrooke Magnanti (1975-11-05) 5 November 1975 (age 48)New Port Richey, Florida, USPen nameBelle de Jour, TaroOccupation Research scientist blogger former call girl Nationality American British Alma materFlorida State University (BS)Sheffield University (PhD)Notable worksThe Intimate Adventures of a London Call GirlWebsitebelledejour.substack.com Brooke Magnanti (born 5 November 1975)[1] is an American-born natura...

George P. PutnamGeorge P. Putnam dan istrinya, Amelia EarhartLahir(1887-09-07)7 September 1887Rye, New YorkMeninggal4 Januari 1950(1950-01-04) (umur 62)Trona, Daerah San Bernardino, California, Amerika SerikatSebab meninggalGagal ginjalKebangsaanAmerikaAlmamaterUniversitas Harvard,Universitas CaliforniaPekerjaanPenerbitPenulisPromotorSuami/istriDorothy Binney (bercerai) Amelia Earhart (janda) Jean-Marie Cosigny James (bercerai)Margaret Havilland (janda)AnakDavid Binney Putnam dan Ge...

Calendar of Armenian Apostolic Church This article has multiple issues. Please help improve it or discuss these issues on the talk page. (Learn how and when to remove these template messages) This article's factual accuracy may be compromised due to out-of-date information. Please help update this article to reflect recent events or newly available information. (March 2011) This article's lead section may be too short to adequately summarize the key points. Please consider expanding the lead ...